## TPRO/TSAT PCI-U-2/-66U SYNCHRONIZABLE TIMECODE GENERATOR with UNIVERSAL PCI BUS INTERFACE

User Manual

95 Methodist Hill Drive Rochester, NY 14623

Phone: US +1.585.321.5800 Fax: US +1.585.321.5219

# www.spectracomcorp.com

Part Number 1186-5001-0050 Manual Revision D 24 April 2009 Copyright © 2009 Spectracom Corporation. The contents of this publication may not be reproduced in any form without the written permission of Spectracom Corporation. Printed in USA.

Specifications subject to change or improvement without notice.

Spectracom, NetClock, Ageless, TimeGuard, TimeBurst, TimeTap, LineTap, MultiTap, VersaTap, and Legally Traceable Time are Spectracom registered trademarks. All other products are identified by trademarks of their respective companies or organizations. All rights reserved.

# SPECTRACOM LIMITED WARRANTY

#### LIMITED WARRANTY

Spectracom warrants each new product manufactured and sold by it to be free from defects in software, material, workmanship, and construction, except for batteries, fuses, or other material normally consumed in operation that may be contained therein AND AS NOTED BELOW, for five years after shipment to the original purchaser (which period is referred to as the "warranty period"). This warranty shall not apply if the product is used contrary to the instructions in its manual or is otherwise subjected to misuse, abnormal operations, accident, lightning or transient surge, repairs or modifications not performed by Spectracom.

The GPS receiver is warranted for one year from date of shipment and subject to the exceptions listed above. The power adaptor, if supplied, is warranted for one year from date of shipment and subject to the exceptions listed above.

THE ANALOG CLOCKS ARE WARRANTED FOR ONE YEAR FROM DATE OF SHIPMENT AND SUBJECT TO THE EXCEPTIONS LISTED ABOVE.

THE TIMECODE READER/GENERATORS ARE WARRANTED FOR ONE YEAR FROM DATE OF SHIPMENT AND SUBJECT TO THE EXCEPTIONS LISTED ABOVE.

The Rubidium oscillator, if supplied, is warranted for two years from date of shipment and subject to the exceptions listed above.

All other items and pieces of equipment not specified above, including the antenna unit, antenna surge suppressor and antenna pre-amplifier are warranted for 5 years, subject to the exceptions listed above.

#### WARRANTY CLAIMS

Spectracom's obligation under this warranty is limited to in-factory service and repair, at Spectracom's option, of the product or the component thereof, which is found to be defective. If in Spectracom's judgment the defective condition in a Spectracom product is for a cause listed above for which Spectracom is not responsible, Spectracom will make the repairs or replacement of components and charge its then current price, which buyer agrees to pay.

Spectracom shall not have any warranty obligations if the procedure for warranty claims is not followed. Users must notify Spectracom of the claim with full information as to the claimed defect. Spectracom products shall not be returned unless a return authorization number is issued by Spectracom.

Spectracom products must be returned with the description of the claimed defect and identification of the individual to be contacted if additional information is needed. Spectracom products must be returned properly packed with transportation charges prepaid.

**Shipping expense:** Expenses incurred for shipping Spectracom products to and from Spectracom (including international customs fees) shall be paid for by the customer, with the following exception. For customers located within the United States, any product repaired by Spectracom under a "warranty repair" will be shipped back to the customer at Spectracom's expense unless special/faster delivery is requested by customer.

Spectracom highly recommends that prior to returning equipment for service work, our technical support department be contacted to provide trouble shooting assistance while the equipment is still installed. If equipment is returned without first contacting the support department and "no problems are found" during the repair work, an evaluation fee may be charged.

EXCEPT FOR THE LIMITED WARRANTY STATED ABOVE, SPECTRACOM DISCLAIMS ALL WARRANTIES OF ANY KIND WITH REGARD TO SPECTRACOM PRODUCTS OR OTHER MATERIALS PROVIDED BY SPECTRACOM, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTY OR MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Spectracom shall have no liability or responsibility to the original customer or any other party with respect to any liability, loss, or damage caused directly or indirectly by any Spectracom product, material, or software sold or provided by Spectracom, replacement parts or units, or services provided, including but not limited to any interruption of service, excess charges resulting from malfunctions of hardware or software, loss of business or anticipatory profits resulting from the use or operation of the Spectracom product or software, whatsoever or howsoever caused. In no event shall Spectracom be liable for any direct, indirect, special or consequential damages whether the claims are grounded in contract, tort (including negligence), or strict liability.

#### **EXTENDED WARRANTY COVERAGE**

Extended warranties can be purchased for additional periods beyond the standard five-year warranty. Contact Spectracom no later than the last year of the standard five-year warranty for extended coverage.

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

# **Table of Contents**

| 1               | OVERVIEW                                                                               | 1 - 1   |

|-----------------|----------------------------------------------------------------------------------------|---------|

| 1.1             | General Information about GPS                                                          | 1-1     |

| 1.2             | Your Spectracom GPS Receiver                                                           |         |

| 1.3             | Distinguishing Between TPRO & TSAT Boards – Software                                   |         |

| 1.4             | Inventory                                                                              |         |

| 1.5             | Inspection and Support                                                                 | 1-2     |

| 2               | SPECIFICATIONS                                                                         |         |

| 2.1             | TPRO (Board Only)                                                                      |         |

| 2.2             | TSAT (GPS Receiver Only)                                                               |         |

| 3               | PINOUTS                                                                                |         |

| 3.1             | Connector Pinout (TSAT Only)                                                           | 3-1     |

| 3.2             | P1 Connector Pinout (TPRO Only)                                                        |         |

| 3.3             | Time Code Input BNC Connector (J1)                                                     |         |

| 3.4             | IRIG-B Output BNC Connector (J2)                                                       |         |

| 4               | CONFIGURATION                                                                          |         |

| 4.1             | Base Address                                                                           |         |

| 4.2             | Interrupt Request Level                                                                |         |

| 4.3             | PCI-U-2/66MHz Jumper Configuration                                                     |         |

| <b>5</b>        | INSTALLATION                                                                           |         |

| 5.1<br>5.2      | GPS Receiver/Antenna (TSAT Only)                                                       |         |

| 5.2<br><b>6</b> | Installing the Board in the Computer <b>BOARD OPERATION</b>                            |         |

| 6.1             | TSAT                                                                                   |         |

| 6.2             | TPRO                                                                                   |         |

| <b>7</b>        | PROGRAMMING FOR TPRO/TSAT-U-2                                                          |         |

| <b>7</b> .1     | General Information                                                                    |         |

| 7.1             | Register Locations                                                                     |         |

| 7.3             | Using the FIFO                                                                         |         |

| 7.4             | Reading Clock Time                                                                     |         |

| 7.5             | Sending Commands                                                                       |         |

| 7.6             | Setting the Clock Time (Not Applicable to Option -M)                                   |         |

| 7.7             | Setting the Clock Time (TPRO Option -M Only)                                           |         |

| 7.8             | Setting the Year (Not Applicable to Option -M)                                         |         |

| 7.9             | Reading the Year, Gregorian Date and Altitude (Not Applicable to Option -M)            | 7-8     |

| 7.10            | Report Longitude (TSAT Only)                                                           |         |

| 7.11            | Report Latitude (TSAT Only)                                                            |         |

| 7.12            | Report Number of GPS Satellites Being Tracked (TSAT Only)                              |         |

| 7.13            | Enable/Disable Sync                                                                    | 7-11    |

| 7.14            | Reading the Status Register                                                            |         |

| 7.15            | Interrupt Control Port                                                                 |         |

| 7.16            | Setting the Propagation Delay Correction                                               |         |

| 7.17            | Setting the Start/Stop ("Match") Times (Not Applicable to Options -FXA, -FXB, or –HDR\ | /) /-13 |

| 7.18            | Programming the Heartbeat Output (Not Applicable to LIPIPPS FYA FYB LOPI Options)      | 714     |

|                 | (Not Applicable to -HB1PPS, -FXA, -FXB, -LOR1 Options)                                 | /-14    |

| 7.19          | Programming the Heartbeat Output (For Options -HB1PPS, -FXA, -FXB, and -LOR1 Only)      |       |

|---------------|-----------------------------------------------------------------------------------------|-------|

| 7.20          | Using the Time Tag Input                                                                |       |

| 7.21          | Report Firmware Version                                                                 |       |

| 7.22          | Clear Flags Port                                                                        |       |

| 7.23          | Reset Firmware                                                                          |       |

| 7.24          | Assert/De-assert Reset                                                                  |       |

| <b>8</b>      | PROGRAMMING THE TPRO/TSAT-66U                                                           |       |

| 8.1           | General Information                                                                     |       |

| 8.2           | Register Locations                                                                      |       |

| 8.3           | Using the FIFO                                                                          |       |

| 8.4           | Reading Clock Time                                                                      |       |

| 8.5           | Sending Commands                                                                        |       |

| 8.6<br>8.7    | Setting the Clock Time (Not Applicable to Option -M)                                    |       |

|               | Setting the Clock Time (TPRO Option -M Only)                                            |       |

| 8.8           | Setting the Year (Not Applicable to Option -M)                                          |       |

| 8.9           | Reading the Year, Gregorian Date and Altitude (Not Applicable to Option -M)             |       |

| 8.10          | Report Logitude (TSAT Only)                                                             |       |

| 8.11          | Report Latitude (TSAT Only)                                                             |       |

| 8.12          | Depart Number of CDS Satellites Doing Tracked (TSAT Only)                               |       |

| 8.13<br>8.14  | Report Number of GPS Satellites Being Tracked (TSAT Only)                               |       |

| 8.15          | Enable/Disable Sync                                                                     |       |

| -             | Reading the Status Register                                                             |       |

| 8.16<br>8.17  | Interrupt Control Port                                                                  |       |

| o. 17<br>8.18 |                                                                                         |       |

|               | Setting the Start/Stop ("Match") Times (Not Applicable to Options -FXA, -FXB, or –HDRV) | 0-13  |

| 8.19          | Programming the Heartbeat Output (Not Applicable to -HB1PPS, -FXA, -FXB, -LOR1 Options) | 0 1 / |

| 8.20          | Programming the Heartbeat Output (For Options -HB1PPS, -FXA, -FXB, and -LOR1 Only)      |       |

| 8.21          | Using the Time Tag Input                                                                |       |

| 8.22          | Report Firmware Version                                                                 |       |

| 8.23          | Report FPGA Version                                                                     |       |

| 8.24          | Clear Flags Port                                                                        |       |

| 8.25          | Reset Firmware                                                                          |       |

| 8.26          | Assert/De-assert Reset                                                                  |       |

| 9<br>9        | OPTIONS AND ACCESSORIES                                                                 |       |

| 9.1           | Options                                                                                 |       |

| 9.1.1         | -DCLOBNC                                                                                |       |

| 9.1.2         | -HB1PPS (Cannot Be Combined with Options -FXA, -FXB, -HDRV)                             |       |

| 9.1.3         | -FXA (TSAT Only; Cannot Be Combined with Options -HB1PPS, -HDRV)                        |       |

| 9.1.4         | -FXB (TPRO Only; Cannot Be Combined with Options -HB1PPS, -HDRV)                        |       |

| 9.1.5         | -LOR1                                                                                   |       |

| 9.1.6         | –M (TPRO Only)                                                                          |       |

| 9.2           | Accessories                                                                             |       |

| 9.2.1         | GPS Optic Isolator                                                                      |       |

| 9.2.2         | GPS Cables                                                                              |       |

| 10            |                                                                                         |       |

# 1 Overview

This manual provides comprehensive information on the system architecture, specifications, and operation of the Spectracom TPRO and TSAT Synchronizable Time Code Generators with Universal PCI Bus Interface.

The TPRO is a precision clock that synchronizes automatically to standardized timecode signals (or, for the TSAT configuration, to the GPS satellite system) and can be read from the PC host computer.

Inputs to the TPRO are modulated timecode (or, for the TSAT, GPS receiver signals), host commands, and time tags.

Outputs are modulated IRIG-B timecode, programmable start/stop time, and a programmable "heartbeat" pulse rate.

The board can generate interrupts on the universal PCI bus (if enabled). Interrupt sources include the heartbeat, time tag, FIFO data available, and at the programmable start time.

The clock automatically synchronizes to specified timecode signals. A status bit advises the host of synchronization status. In the absence of timecode input or GPS, the board starts counting at 000 days, 00 hours, 00 minutes, 00 seconds at power-on. The clock time can also be set by user command.

#### 1.1 General Information about GPS

**NOTE:** GPS applies only to the TSAT board. The TPRO is not equipped for GPS.

The United States government operates a set of approximately 32 satellites, collectively known as the "GPS Constellation" or "GPS Satellites." Each satellite has an internal atomic clock and transmits a signal specifying the time and satellite position. On the ground, the GPS receiver determines its position (longitude, latitude, and elevation) and the time by decoding the signals simultaneously from at least four of the GPS satellites.

The satellite orbits are circular, inclined approximately 56 degrees from the equator, orbiting the Earth once every 11 hours. There are several different orbital planes, providing continuous coverage to all places on Earth. The GPS receiver uses an omni-directional antenna; the satellites move slowly across the sky (they are not at fixed locations).

Each satellite transmits a spread-spectrum signal, centered at 1575.42 MHz. When power is first applied, the GPS receiver begins searching for the satellites. It does this by searching for each satellite individually, listening for each satellite's distinct spread-spectrum hopping sequence. This process can take a few minutes, as the receiver iteratively locates satellites, refines its position, and determines for which satellites to search.

The GPS receiver retains the last known position when the power is switched off. This results in faster satellite acquisition the next time it is switched on. If the antenna has been moved more than a few miles, however, acquisition time will be slightly longer because it must first recompute the position.

## 1.2 Your Spectracom GPS Receiver

Your board's GPS receiver is built into the antenna housing and communicates to the board via a serial (RS-422) interface. Power (+12V) is supplied from the board. The unit comes with a 100-foot cable. Extension cables are available in 100-foot lengths. The maximum total length is 500 feet. The connectors on the extension cables are not weatherproof; only the first 100-feet can be outdoors. The cable consists of several twisted pairs (not coaxial cable) and a foil shield.

**NOTE:** Spectracom recommends applying an appropriate silcon grease to the cable connection at the GPS antenna in order to protect the connection from moisture. An additional weatherproofing kit (P/N 221213) containing butyl rubber and plastic tape is also available from Andrews Corporation, US 800.255.1479.

## 1.3 Distinguishing Between TPRO & TSAT Boards – Software

Examine the Subsystem Product ID number that is detailed in the "Specifications" section.

# 1.4 Inventory

Before installing the board, please verify that all material ordered has been received. The TSAT is delivered with a 100-foot cable with pre-installed connectors, a GPS receiver/antenna (housed together in a single enclosure), and a user manual. The TPRO is delivered with mating connector (15-pin) and a user manual. If there is a discrepancy, please contact Spectracom Customer Service at US 585.321.5800.

# 1.5 Inspection and Support

Unpack the equipment and inspect it for damage. If any equipment has been damaged in transit, please contact Spectracom Customer Service at US 585.321.5800.

If any problems occur during installation and configuration of your Spectracom product, please contact Spectracom Technical Support at US 585.321.5823 or US 585.321.5824.

#### **CAUTION:**

Electronic equipment is sensitive to Electrostatic Discharge (ESD). Observe all ESD precautions and safeguards when handling the timecode generator.

**NOTE:** If equipment is returned to Spectracom, it must be shipped in its original packing material. Save all packaging material for this purpose.

# 2 Specifications

**NOTE:** In this manual, the prefix "0x" indicates that the number is in hexadecimal (Base 16) format.

# 2.1 TPRO (Board Only)

| Table 2.1—Time Code Input Specifications |                                                      |  |

|------------------------------------------|------------------------------------------------------|--|

| Code Format (autodetect)                 | IRIG-A (A132)*, IRIG-B (B122), NASA36                |  |

| Amplitude                                | 1.2 Vp-p min, 8.0 Vp-p max                           |  |

| Polarity                                 | Detected automatically                               |  |

| Modulation Ratio                         | 2:1 min, 3:1 typical, 4:1 max                        |  |

| Input Impedance                          | >10 K ohms                                           |  |

| Timing Accuracy                          | Better than 100 ppm (not suitable for tape playback) |  |

| Common Mode Voltage                      | Differential input, ±100 V max                       |  |

<sup>\*</sup>Not supported with Option -M.

| Table 2.2—IRIG-B Output Specifications |                 |

|----------------------------------------|-----------------|

| Code Format                            | IRIG-B (B122)   |

| Amplitude (mark)                       | 3.5 Vp-p (type) |

| Modulation Ratio                       | 3:1             |

| Output Impedance                       | 600 ohms        |

| Table 2.3—Time Tag Input Specifications |                                                                                         |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------|--|

| Input Voltage                           | -0.5V min, +0.8V max for logic 0<br>+2.0V min, +5.5 max for logic 1<br>Tags rising edge |  |

| Input Current                           | <5 μA for logic 0<br><5 μA for logic 1                                                  |  |

| Rise/Fall Time                          | 500 nS max                                                                              |  |

| Repetition Rate                         | 1000 events per second max                                                              |  |

| Timing Resolution                       | 1 μS                                                                                    |  |

| Table 2.4—1 PPS Sync Input Specifications (Option -M Only) |                                                                            |  |

|------------------------------------------------------------|----------------------------------------------------------------------------|--|

| Input Voltage                                              | 2.4 V min, 16.0 V max (high)<br>(500 μA max at 5 Vin, 12 mA max at 16 Vin) |  |

| Rise/Fall Time                                             | 500 nS max                                                                 |  |

| Trigger Edge                                               | Rising                                                                     |  |

| 1PPS <sup>H</sup> Accuracy                                 | Must be 100 ppm or better                                                  |  |

H One pulse-per-second

| Table 2.5—Match Output Specifications |                                                      |

|---------------------------------------|------------------------------------------------------|

| Output Voltage                        | 3.8 V min at 6 mA (high)<br>0.4 V max at -6 mA (low) |

| Setability                            | 1 μS                                                 |

| Table 2.6—On-board Clock Specifications |                                                                               |  |

|-----------------------------------------|-------------------------------------------------------------------------------|--|

| Resolution                              | 1 μS                                                                          |  |

| Range                                   | 366:23:59:59.999999                                                           |  |

| Date Format                             | Integer (001-366)                                                             |  |

| Synchronization Time                    | <8 seconds                                                                    |  |

| Stability                               | Disciplined to timecode: 1x10 <sup>-6</sup> Undisciplined: 2x10 <sup>-7</sup> |  |

| Table 2.7—PCI Interface Specifications                                                                                 |                                                                                         |                                                                                         |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Model                                                                                                                  | PCI-U-2                                                                                 | PCI-66U                                                                                 |

| Interface                                                                                                              | PCI Spec. 2.2                                                                           | 2 compliant                                                                             |

| Bus Speed                                                                                                              | 33MHz                                                                                   | 33/66MHz                                                                                |

| I/O                                                                                                                    | 64 by                                                                                   | rtes                                                                                    |

| DMA Transfers                                                                                                          | Nor                                                                                     | ne                                                                                      |

| General                                                                                                                | Occupies 32 consecutive 16-bit I/O and memory addresses (64 bytes)                      |                                                                                         |

| Chipset Vendor ID                                                                                                      | 0x10b5                                                                                  | 0x1AD7                                                                                  |

| Chipset Product ID                                                                                                     | 0x9030                                                                                  | 0x9100                                                                                  |

| Subsystem Vendor ID                                                                                                    | 0x1347                                                                                  | 0x1AD7                                                                                  |

| Subsystem Product ID TPRO-PCI TPRO-PCI-M TPRO-PCI-HB1PPS TPRO-PCI-FXB TPRO-PCI-LOR1 TPRO-PCI-M-HB1PPS TPRO-PCI-DCLOBNC | 0x9050 (standard)<br>0x9051<br>0x9052<br>0x9052<br>0x9052<br>0x9052<br>0x9053<br>0x9050 | 0x9150 (standard)<br>0x9151<br>0x9152<br>0x9152<br>0x9152<br>0x9152<br>0x9153<br>0x9150 |

| TSAT-PCI<br>TSAT-PCI-HB1PPS<br>TSAT-PCI-FXA<br>TSAT-PCI-DCLOBNC                                                        | 0x9070 (standard)<br>0x9072<br>0x9072<br>0x9072                                         | 0x9170 (standard)<br>0x9172<br>0x9172<br>0x9172                                         |

| Table 2.8—General Specifications |                                                                                                                                                |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Size                             | H 106.7 mm, L 174.6 mm (H 4.2", L 6.875")                                                                                                      |  |

| Power (from PCI bus)             | +5 VDC @ 425 mA max,<br>+12 VDC @ 225 mA max,<br>-12 VDC @ 50 mA max                                                                           |  |

| Operating Temperature            | -30 to +70 C (-22 to +158 F)                                                                                                                   |  |

| Storage Temperature              | -40 to +80 C (-40 to +176 F)                                                                                                                   |  |

| Connectors                       | BNCs for timecode input and output; DB15 (socket) for timecode input, output, heartbeat output, match output, time-tag input, and 1 PPS input. |  |

| Table 2.9—Heartbeat Output Specifications |                                                       |  |

|-------------------------------------------|-------------------------------------------------------|--|

| Output Voltage                            | 3.8 V min at 6 mA (high)<br>0.4 V max at -6 mA (low)  |  |

| Wave Shape                                | Pulse or Square Wave (programmable)                   |  |

| Pulse Width                               | 150 nS min, 450 nS max                                |  |

| Pulse Polarity                            | Negative                                              |  |

| Square Wave                               | 45% - 55%                                             |  |

| Timing                                    | Falling edge on-time (pulse or square wave)           |  |

| Range                                     | 1.000 μS-21.845 mS in 1 μS steps (1 MHz - 45.7771 Hz) |  |

| Power-on default rate                     | 100 PPS (pulse)                                       |  |

# 2.2 TSAT (GPS Receiver Only)

**NOTE:** When both IRIG and GPS synchronization sources are connected simultaneously, the unit will default to IRIG decoding.

| Table 2.10—GPS Receiver/Antenna Specifications |                                                                                                        |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Number of Satellites                           | 6                                                                                                      |  |

| Acquisition Time (cold start)                  | 1 minutes typical                                                                                      |  |

| Re-acquisition Time                            | <1 minute                                                                                              |  |

| Frequency                                      | L1 frequency, C/A code (SPS), continuous tracking receiver, static overdetermined clock mode (default) |  |

| Sync to UTC                                    | Within 15 nanoseconds (static)                                                                         |  |

| Accuracy Horizontal Position                   | <6 meters (50%) <9 meters (90%)                                                                        |  |

| Accuracy Altitude Position                     | <11 meters (50%) <18 meters (90%)                                                                      |  |

| Altitude                                       | 0 m to +18,000 m (0 to +59,055 feet)                                                                   |  |

| Size                                           | 3.74" D, 2.85" H (95mm x 72.5mm)                                                                       |  |

| Weight                                         | 5.4 oz (154 g)                                                                                         |  |

| Pole Mount                                     | 1"-14 straight thread or 3/4" pipe thread                                                              |  |

| Operating Temp                                 | -40° to +85° C (-40 to +185 °F)                                                                        |  |

| Storage Temp                                   | –55° to +105° C (-67 to +221 °F)                                                                       |  |

| Operating Humidity                             | 95% RH, non-condensing @ 60 °F                                                                         |  |

# 3 Pinouts

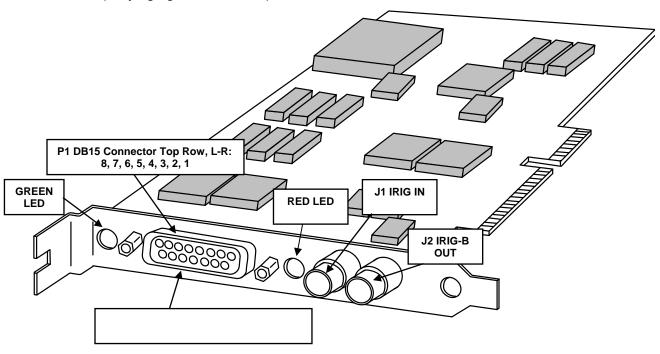

The accompanying figure illustrates pinouts for both the TSAT-PCI and the TPRO-PCI:

# 3.1 Connector Pinout (TSAT Only)

The GPS receiver/antenna cable plugs into the 15-pin P1 connector. In addition, some pins may interface to the user's equipment. It is the user's responsibility to modify the antenna cable connector, if necessary, to access the "User Connection" pins. A description of the pinout for the supplied cable is shown in Table 3.1. Refer to the figure on the following page.

| Table 3 | Table 3.1—TSAT, P1 Connector Pinout |                    |              |                   |  |

|---------|-------------------------------------|--------------------|--------------|-------------------|--|

| P1 Pin  | Antenna Pin                         | Antenna Connection | Wire Color   | User Connection   |  |

| 1       |                                     |                    |              | Do not connect    |  |

| 2       |                                     |                    |              | Do not connect    |  |

| 3       | 1                                   | +12 Volts          | Red          |                   |  |

| 4       |                                     |                    |              | Time Tag input    |  |

| 5       | 9                                   | Ground             | Black        | Ground            |  |

| 6       |                                     |                    |              | Heartbeat output  |  |

| 7       |                                     | Ground             | Shield       |                   |  |

| 8       |                                     |                    |              | Match time output |  |

| 9       | 11                                  | 1PPS+              | Orange/White |                   |  |

| 10      | 5                                   | RXD+               | Yellow       |                   |  |

| 11      | 4                                   | RXD-               | Brown        |                   |  |

| 12      | 3                                   | TXD+               | Orange       |                   |  |

| 13      | 2                                   | TXD-               | Violet       |                   |  |

| 14      | 12                                  | 1PPS-              | Black/White  |                   |  |

| 15      | 8                                   | Battery            | Green        |                   |  |

The antenna cable wires are twisted pairs as follows:

| Red with Black                | (Pins 3 and 5)     |

|-------------------------------|--------------------|

| Orange with Violet            | (Pins 12 and 13)   |

| Yellow with Brown             | (Pins 10 and 11)   |

| Green with Blue               | (Pins 15 and None) |

| Orange/White with Black/White | (Pins 9 and 14)    |

**NOTE:** The following antenna cable wires are connected at the antenna end, but NOT at P1:

| Antenna | Pin Color |

|---------|-----------|

| 6       | White     |

| 7       | Gray      |

| 10      | Blue      |

The pigtail on the 15-pin end of the cable is used for custom options (if any).

# 3.2 P1 Connector Pinout (TPRO Only)

The timecode input can be applied either to Pins 1 and 2 of P1 or to the J1 BNC connector (this is the connector closest to P1). The timecode input is a differential signal (i.e., timecode input is isolated from ground). It is acceptable to connect timecode input to ground.

The IRIG-B output can be taken either from Pin 9 of P1 or from the J2 BNC connector (this is the connector farthest from P1). The IRIG-B output is a single-ended signal (i.e., it is referenced to ground).

| Table 3 | Table 3.2—TPRO, P1 Connector Pinout |                          |   |  |

|---------|-------------------------------------|--------------------------|---|--|

| P1 Pin  | User Connection                     | Other Options            |   |  |

| 1       | IRIG IN +                           |                          |   |  |

| 2       | IRIG IN -                           | _                        |   |  |

| 3       | Do not use                          |                          |   |  |

| 4       | Time Tag input                      |                          |   |  |

| 5       | Ground                              |                          |   |  |

| 6       | Heartbeat output                    | FXB + / HB1PPS+ / HDRV + | * |  |

| 7       | Ground                              |                          |   |  |

| 8       | Match time output                   | FXB - / HDRV -           | * |  |

| 9       | IRIG B Output                       | DCLOBNC                  | * |  |

| 10      | <del></del>                         |                          |   |  |

| 11      |                                     |                          |   |  |

| 12      |                                     |                          |   |  |

| 13      |                                     |                          |   |  |

| 14      |                                     |                          |   |  |

| 15      | 10 MHz output                       | Option M                 | * |  |

<sup>\*</sup> Refer to Section 9, Options and Accessories, for more information.

# 3.3 Time Code Input BNC Connector (J1)

The timecode input BNC connector is located nearest the 15-pin D-type connector.

# 3.4 IRIG-B Output BNC Connector (J2)

The IRIG-B output BNC connector is located farthest from the 15-pin D-type connector.

# 4 Configuration

#### 4.1 Base Address

The host computer's PCI BIOS software configures the base address.

# 4.2 Interrupt Request Level

The host computer's PCI BIOS software configures the interrupt request (IRQ) level.

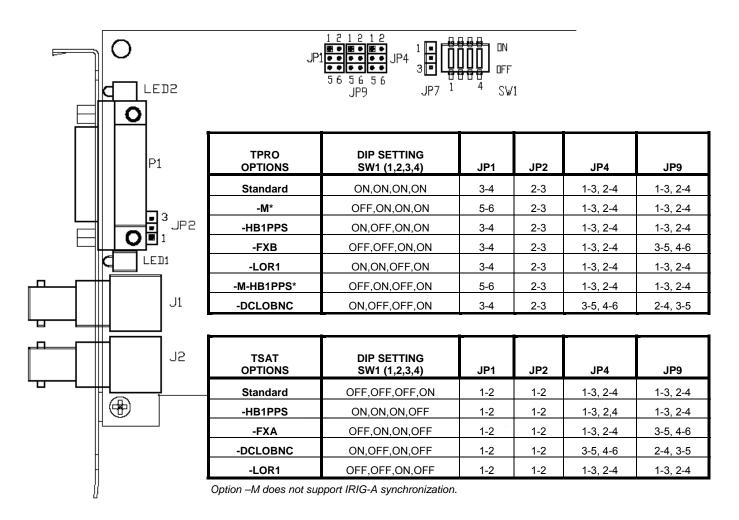

# 4.3 PCI-U-2/66MHz Jumper Configuration

## 5 Installation

## 5.1 GPS Receiver/Antenna (TSAT Only)

The mounting location should be free of objects that could obstruct satellite visibility from straight overhead to within 20 degrees of the horizon in all directions. Obstructions that block a significant portion of the sky result in degraded performance. Specifically, the GPS receiver can track fewer than four satellites, which would prevent it from obtaining time synchronization. To optimize timing accuracy, the GPS receiver attempts to track satellites that are spread out as far as possible across the sky. The GPS receiver/antenna must be mounted with the connector side pointing down and must be spaced at least 39 inches (1 meter) away from other GPS antennas.

Mount the antenna at the desired location. Connect the round end of the supplied cable to the antenna. Take appropriate lightning precautions as necessary.

**NOTE:** Spectracom recommends applying an appropriate silcon grease to the cable connection at the GPS antenna in order to protect the connection from moisture. An additional weatherproofing kit (P/N 221213) containing butyl rubber and plastic tape is also available from Andrews Corporation, US 800.255.1479.

# 5.2 Installing the Board in the Computer

Shut the computer down, then turn its power switch off and unplug the line cord.

Open the computer and install the board in any unused PCI slot.

#### **CAUTION:**

Observe all ESD procedures when handling the board and the computer. Before installing the board, discharge static buildup by touching the metal frame of the computer with one hand and the protective bag containing the board with the other hand. Open the protective bag only after static buildup has been safely discharged.

Remove the metal plate at the desired location on the rear panel, then plug the board in. Attach the top of the mounting bracket with the screw from the metal plate.

Close the computer, plug in the line cord, start the computer. Depending on which operating system being used, a message that identifies new hardware may appear; this message may indicate that the hardware is of "unknown type." This is normal. Exit the "Found New Hardware" dialogue box. **DO NOT click on "Have Disk."**

The TPRO and TSAT operate automatically as soon as the host computer system performs the power-on reset. To change the operating parameters or read data, consult Chapter Seven.

An on-board LED (LED1) flashes a status pattern to assist in diagnosing installation errors. The pattern is a sequence of short and long flashes. To enable the status pattern to repeat more frequently, trailing short flashes are deleted.

| Table 5.1—LED Flash Patterns |                                                                                                  |                                                                                                                                                                          |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Flash Position               | Meaning of Short (Cleared) Flash                                                                 | Meaning of Long (Set) Flash                                                                                                                                              |  |  |

| 1                            | GPS satellite receiver being used for time reference                                             | Modulated timecode input being used for time reference                                                                                                                   |  |  |

| 2                            | Synchronization to better than 5μs verified with last 5 seconds                                  | Synchronization to better than 5μs not verified within last 5 seconds                                                                                                    |  |  |

| 3                            | 1PPS pulse from GPS satellite receiver is OK                                                     | 1 PPS pulse from GPS satellite receiver is bad. In applications with modulated timecode inputs only, this status bit will always be set.                                 |  |  |

| 4                            | GPS satellite receiver serial data being received OK                                             | No serial data being received from GPS satellite receiver. In applications with modulated timecode inputs only, this status bit will always be set.                      |  |  |

| 5                            | GPS satellite receiver is tracking enough satellites for accurate UTC time.                      | GPS satellite receiver is not tracking enough satellites for accurate UTC time. In applications with modulated timecode inputs only, this status bit will always be set. |  |  |

| 6                            | Timecode input being decoded                                                                     | Timecode input not decodable. In applications without modulated timecode inputs, this status bit will always be set.                                                     |  |  |

| 7                            | If using 1PPS, set NEXT 1PPS TIME command sequence has been performed. (Used for Option –M only) | Waiting for "SET NEXT 1PPS TIME" command. (Used for Option –M only)                                                                                                      |  |  |

# 6 Board Operation

#### **6.1 TSAT**

The TSAT acquires time from the GPS satellites, synchronizes its on-board clock to this time, and provides an IRIG-B output from the on-board clock.

**NOTE:** When IRIG and GPS are connected simultaneously, the unit defaults to IRIG synchronization.

GPS consists of a set ("constellation") of approximately 30. These satellites are in relatively high, circular orbits, are inclined about 55 degrees relative to the equator, and circle the Earth approximately once every 12 hours. Consequently, several satellites are above the horizon at all times anywhere on Earth. The receiver must track at least four satellites simultaneously in order to determine time and position. Best accuracy is achieved when the satellites that are being tracked are scattered widely across the sky; the receiver automatically attempts to choose satellites based on maximum apparent separation. Therefore, it is important that the antenna have a clear view of as much sky as possible (and, for the same reason, be mounted with the connector pointed down). The satellites do not remain at a fixed location in the sky.

Occasionally, the receiver stops tracking a satellite and begins searching for another one; this causes fluctuations in the number of satellites tracked (between five and eight).

The most common complaint among new GPS users is that the time needed to begin tracking satellites varies each time the unit is turned on, or that it seems to take a long time to begin tracking. Refer to the section entitled "Specifications" in Chapter Two for typical and maximum times, and note that significant variations around the "typical" time are normal. If the receiver has not established synchronization after the maximum time specified, the most probable reason is that the antenna does not have an unobstructed view of the sky—try re-locating the antenna. Note that the GPS receiver is built into the antenna housing; additional filtering cannot be installed.

When power is applied, the GPS receiver automatically begins to search for GPS satellite signals. After the receiver has been operating for a few minutes and has calculated the position (longitude, latitude, and altitude), it saves the position in memory. A saved position results in faster re-acquisition the next time power is applied. A large capacitor on the board provides voltage to the receiver's memory; if the cable between the board and the receiver is disconnected, or if the computer has not been turned on in approximately the past 10 days, the receiver's position memory is lost. Therefore, a slightly longer acquisition time is required the next time that power is applied.

The time obtained is in Coordinated Universal Time (UTC) format. This means the same time (and date) is received in all parts of the world, regardless of local time zone. UTC is 5 hours ahead of Eastern Standard Time (EST) in the United States in winter, and 4 hours ahead of Eastern Daylight Time (EDT) in summer. UTC is not adjusted for Daylight Saving time; for example, 10:00 p.m. in New York City on July 3rd is 02:00 a.m. July 4th UTC.

A Gregorian date consists of the year, month, and day in the format YYYY-MM-DD; for example, "2003-09-19" for September 19, 2003. The Gregorian date can be read from the board; however, the Gregorian date is not transmitted in the IRIG-B output. Instead, the IRIG-B

output transmits the Julian date (an integer from 001-366 that represents the day number in the year). This limitation is due to the standard definition of the IRIG-B code format.

The on-board clock continues to increment time ("freewheel") while not tracking satellites. When power is first applied, time begins freewheeling from 000:00:00:00, then jumps to the correct time when synchronization is established.

#### 6.2 TPRO

The TPRO acquires time from the timecode input, synchronizes its on-board clock to this time, and provides an IRIG-B output from its on-board clock. The timecode input consists of an amplitude-modulated sine wave (carrier frequency is 1 kHz for IRIG-B or NASA36, or 10 kHz for IRIG-A). The code format is detected automatically.

The board does not significantly load the timecode input, and, since it is a very low frequency, cable impedance mismatches do not significantly degrade the signal either. Thus, a single timecode source can drive at least 10 inputs. Cable termination is not necessary, cable length can be up to several hundred feet, and a variety of cable types can be used. Usually, coaxial cable (RG-58 or RG-59 type) with BNC connectors is used. Multiple boards can be driven by placing a BNC "T" connector at each board, and connecting the timecode input in a daisy-chain configuration.

For another approach, take the IRIG-B output from one board to the timecode input of the next board (i.e., a loop-through configuration). The advantage of the loop-through configuration is that if the signal is lost at some point, all boards downstream of the break continue to have the same time (driven by the first board's freewheeling clock). Also, it eliminates the need for BNC "T" connectors.

The board synchronizes to the incoming timecode automatically. An on-board 10 MHz crystal oscillator is phase-locked to the timecode carrier frequency. This results in timing resolution down to  $1\mu S$ , despite the fact that the input carrier is only 1 kHz (or 10 kHz for IRIG-A). Also, this precludes using timecode from sources with unstable time bases (e.g., playback from tape or digital storage).

By definition, the timecode format standard (IRIG-B, NASA36, or IRIG-A) specifies that the format for transmitting the date be an integer (001-366). This is referred to as the Julian date. Note that the date is not in year/month/day as in Gregorian format.

**NOTE:** Although the user's software can convert from a Julian date to a Gregorian date, be careful. First, the user's software must distinguish whether or not the current year is a leap year. Second, the user's software must account for the fact that, when freewheeling before synchronizing, the board will report an invalid Julian date (000).

# 7 Programming for TPRO/TSAT-U-2

#### 7.1 General Information

From a programming standpoint, the board appears to be a PCI-to-ISA bridge device. This means that the universal PCI bus "sees" the board as a device that has thirty-two consecutive 16-bit memory locations (64 bytes) and thirty-two consecutive 16-bit I/O locations (64 bytes). During startup, the PCI BIOS (part of the host computer) mapped these locations somewhere in the absolute address space.

The thirty-two memory locations and the thirty-two I/O locations serve exactly the same functions. In actual use, only one of these (either memory or I/O) is used; the other is ignored. On host computers with Intel CPUs (e.g., Pentium, 486, etc.) use the I/O locations. On host computers with Motorola CPUs (e.g., the 68000 family) use the memory locations (since Motorola does not have "I/O" instructions).

The locations of the board's registers are specified as "Base + Offset". The offsets are constants, as described in the next section. The "Base" is chosen by the PCI BIOS during startup. There is a separate "Base" for the memory and I/O locations.

Time is read as four 16-bit words, and is in binary-coded decimal format. Status is read as a single 16-bit word. Time tags and, for the TSAT, GPS information (longitude, latitude, altitude, and Gregorian date), are read by first sending a command to the board, then reading ten 16-bit words from a first-in-first-out (FIFO) register.

The user's software must wait a short amount of time after sending each command. This admittedly cumbersome requirement is necessary because the on-board processor places a higher priority on maintaining the time than on processing commands. The actual amount of time needed to process a command depends on when the command was received relative to the on-board time. Entries in Chapter Six specify the amount of time needed to assure that the command was received. There is no restriction on reading from the board.

Each 16-bit word is located on an even address. Although many of the registers use only eight bits, always read and write registers as 16-bit entities. **Do not attempt an 8-bit access on an odd address location.**

# 7.2 Register Locations

**NOTE:** In this manual, the prefix "0x" indicates that the number is in hexadecimal (Base 16) format.

| Table 7.1—Register Locations for PRO/TSAT-U-2 |                                 |                           |                                                                               |  |  |

|-----------------------------------------------|---------------------------------|---------------------------|-------------------------------------------------------------------------------|--|--|

| Location                                      | Read Usage                      | Write Usage               | Register Function                                                             |  |  |

| Base + 0x00                                   | FIFO                            | Interrupt Control<br>Port | R - Returns response data from the board W - Interrupt control register       |  |  |

| Base + 0x02                                   | Status Register                 | Command Port              | R - Returns status information for the board W - Issues commands to the board |  |  |

| Base + 0x04                                   | Н                               | De-assert Reset           | Releases the board from reset                                                 |  |  |

| Base + 0x06                                   | Н                               | Assert Reset              | Places the board into reset                                                   |  |  |

| Base + 0x08                                   | Clock: Days                     | Н                         | Returns portion of latched time                                               |  |  |

| Base + 0x0a                                   | Clock: Hours,<br>Minutes        | Н                         | Returns portion of latched time                                               |  |  |

| Base + 0x0c                                   | Clock: Seconds<br>through 10 mS | Н                         | Returns portion of latched time                                               |  |  |

| Base + 0x0e                                   | Clock: 1 mS through 1 uS        | Н                         | Latches a snapshot of the present time and returns the lower portion of time  |  |  |

| Base + 0x10                                   | Н                               | Clear Flags               | Clears interrupt flags                                                        |  |  |

| Base + 0x12                                   | Н                               | Simulate Time Tag         | Simulates a time tag occurrence                                               |  |  |

| Base + 0x14                                   | Н                               | Н                         |                                                                               |  |  |

| Base + 0x16                                   | Н                               | Н                         |                                                                               |  |  |

| (H = Reserved for future use.)                |                                 |                           |                                                                               |  |  |

## 7.3 Using the FIFO

The board uses a FIFO register to provide multi-word responses. Each of these responses consists of ten 16-bit words, of which only the lower 8-bits are actually used. A bit in the Status Register indicates whether data is ready in the FIFO. The user's software must check that status bit before reading *each* word from the FIFO.

There can be a delay of up to 200  $\mu$ S before all ten words are written into the FIFO. This is due to the fact that although the on-board CPU writes this data, it also maintains the time (days through milliseconds) in software, and places a higher priority on maintaining the time than on filling the FIFO. Thus, it is not uncommon that, for example, only three of the ten words are written into the FIFO, then, following a substantial delay, the remaining seven words are written. The user's software must allow for such operation (i.e., it must not "give up" just because it has not read all ten words before the status indicates that the FIFO is empty. Either wait 200  $\mu$ S before beginning to read, or allow for enough retries if FIFO empty status is detected prematurely.)

To check the FIFO Ready flag, read the Status Register (at Base + 0x02). If the least significant bit is a zero, there is data in the FIFO. If this bit is a one, the FIFO is empty.

The FIFO holds 512 words (i.e., 51 responses). Letting these responses stack up in the FIFO is acceptable, but the user's software is responsible for knowing what each of the responses is.

During initialization, the user's software must flush the FIFO. Do this by reading the FIFO until the "FIFO Ready" flag is a one. This could take up to 512 reads, maximum.

Responses to user commands echo the command in the first two words from the FIFO. This can be useful in sorting out multiple responses that are stacked up in the FIFO.

# 7.4 Reading Clock Time

The current ("clock") time is read as four 16-bit words. Reading the first word latches all four words, thus the latency time between reading them does not affect the accuracy. This also means that it is important to read the least significant word first, as this causes the other words to be latched. It is not necessary to read all four words if the application does not need the complete clock time.

**NOTE:** These locations are read-only. A different sequence is used to set the time. Refer to the sections on setting the clock time.

It is also necessary to examine the status register to determine if the time is valid.

The Julian date (not the Gregorian date) is reported.

The value range for Days is 000-366. Be sure the variable that stores Days can accommodate this range. Assigning Days to an 8-bit integer (with a range of 000-255) produces an unpleasant surprise in mid-September!

Within each 16-bit word there are four "nibbles" (groupings of 4 bits each). Each nibble is decoded separately, representing a single binary-coded-decimal (Base 10) digit.

| Table 7.2—Clock Time Data |                         |                         |                         |                          |  |

|---------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--|

| Location                  | Most Significant Nibble | Nibble                  | Nibble                  | Lease Significant Nibble |  |

| Base + 0x0e               | 10 <sup>0</sup> mS      | 10² μS                  | 10 <sup>1</sup> μS      | 10 <sup>0</sup> μS       |  |

| Base + 0x0c               | 10 <sup>1</sup> Seconds | 10 <sup>0</sup> Seconds | 10 <sup>2</sup> mS      | 10 <sup>1</sup> mS       |  |

| Base + 0x0a               | 10 <sup>1</sup> Hours   | 10 <sup>0</sup> Hours   | 10 <sup>1</sup> Minutes | 10 <sup>0</sup> Minutes  |  |

| Base + 0x08               | (Reserved)              | 10 <sup>2</sup> Days    | 10 <sup>1</sup> Days    | 10 <sup>0</sup> Days     |  |

For example, if the time is day 123, hour 11, minute 58, second 17.654321, the time is read as follows:

| Location    | Contents |               |

|-------------|----------|---------------|

| Base + 0x0e | 0x4321   |               |

| Base + 0x0c | 0x1765   |               |

| Base + 0x0a | 0x1158   |               |

| Base + 0x08 | 0xU123   | (U = Unknown) |

## 7.5 Sending Commands

Writing to the Command Port at Base + 0x02, sends commands to the board. A small delay is required after sending each word. Note that there is no way to "read back" a command once it has been sent.

Commands consist of one or more 16-bit words, of which only the lower 8-bits are actually used. These lower 8 bits are further divided into two 4-bit "nibbles". For some commands, the high nibble is a constant, and the low nibble contains the data. For other commands both the high and low nibbles are constant.

It is necessary to wait at least 100  $\mu S$  after sending each command word before sending anything else to the command port.

| Table 7.3—Command Functions                                                                             |           |  |  |

|---------------------------------------------------------------------------------------------------------|-----------|--|--|

| Function                                                                                                | Command   |  |  |

| Reset Firmware                                                                                          | 0x004f    |  |  |

| Enable Sync                                                                                             | 0x004d    |  |  |

| Disable Sync                                                                                            | 0x004e    |  |  |

| Report Firmware Version in FIFO                                                                         | 0x00e9    |  |  |

| Report Number of GPS Satellites in FIFO (TSAT only)                                                     | 0x005c    |  |  |

| Report Altitude & Gregorian Date in FIFO                                                                | 0x005d    |  |  |

| Report Longitude in FIFO (TSAT only)                                                                    | 0x005e    |  |  |

| Report Latitude in FIFO (TSAT only)                                                                     | 0x005f    |  |  |

| Clear Holding Register                                                                                  | 0x00f0    |  |  |

| Put 10 <sup>2</sup> Days in Holding Register                                                            | 0x0050-53 |  |  |

| Put 10 <sup>1</sup> Days in Holding Register                                                            | 0x0060–69 |  |  |

| Put 10 <sup>0</sup> Days in Holding Register                                                            | 0x0070–79 |  |  |

| Put 10 <sup>1</sup> Hours or 10 <sup>-1</sup> Seconds in Holding Register                               | 0x0080–89 |  |  |

| Put 10 <sup>0</sup> Hours or 10 <sup>-2</sup> Seconds in Holding Register                               | 0x0090–99 |  |  |

| Put 10 <sup>1</sup> Minutes, 10 <sup>-3</sup> Seconds, or 16 <sup>3</sup> Heartbeat in Holding Register | 0x00a0-af |  |  |

| Put 10 <sup>0</sup> Minutes, 10 <sup>-4</sup> Seconds, or 16 <sup>2</sup> Heartbeat in Holding Register | 0x00b0-bf |  |  |

| Put 10 <sup>1</sup> Seconds, 10 <sup>-5</sup> Seconds, or 16 <sup>1</sup> Heartbeat in Holding Register | 0x00c0-cf |  |  |

| Put 10 <sup>0</sup> Seconds, 10 <sup>-6</sup> Seconds, or 16 <sup>0</sup> Heartbeat in Holding Register | 0x00d0-df |  |  |

| Put Propagation Delay 10 <sup>3</sup> μS in Holding Register                                            | 0x0030–39 |  |  |

| Put Propagation Delay 10 <sup>2</sup> μS in Holding Register                                            | 0x0020–29 |  |  |

| Put Propagation Delay 10 <sup>1</sup> μS in Holding Register                                            | 0x0010–19 |  |  |

| Put Propagation Delay 10 <sup>0</sup> μS in Holding Register                                            | 0x0000-09 |  |  |

| Copy Holding Register to Clock Time or Propagation Time                                                 | 0x00e0    |  |  |

| Copy Holding Register to Start/Stop Time (Days-Seconds)                                                 | 0x00e1    |  |  |

| Copy Holding Register to Start Time (10 <sup>-1</sup> to 10 <sup>-6</sup> Seconds)                      | 0x00e2    |  |  |

| Copy Holding Register to Stop Time (10 <sup>-1</sup> to 10 <sup>-6</sup> Seconds)                       | 0x00e3    |  |  |

| Copy Holding Register to Clock Time on next 1PPS (Option –M only)                                       | 0x004c    |  |  |

| Copy Holding Register to Heartbeat, Pulse Mode, at next period                                          | 0x00e5    |  |  |

| Copy Holding Register to Heartbeat, Pulse Mode, immediately                                             | 0x00e6    |  |  |

| Copy Holding Register to Heartbeat, Square wave Mode, at next period                                    | 0x00e7    |  |  |

| Copy Holding Register to Heartbeat, Square wave Mode, immediately                                       | 0x00e8    |  |  |

| Copy Holding Register to Year                                                                           | 0x00ea    |  |  |

# 7.6 Setting the Clock Time (Not Applicable to Option -M)

Set the clock time by commanding the days, hours, minutes, and seconds. The milliseconds and microseconds cannot be commanded; they are reset to 000000 when the command is sent.

It is necessary to load the time into the Holding Register. First, send a command to clear the Holding Register. Then, one at a time, write each digit (hundreds of days down to ones of seconds) into the Holding Register.

There is a separate command for loading each of these digits. The upper 4 bits of the command identify which digit is being loaded, the lower 4 bits contain the actual data to load. Once all the digits have been loaded, a command is sent to set the time (the board does this by copying the Holding Register into the clock).

For example, to set the clock to day 123, hour 11, minute 58, second 17, send the following sequence of commands to the Command Port:

```

0x00f0

; Clear the Holding Register

0x0051

0x0073

0x0062

; Day 123

; Hour 11

0 \times 0081

0x0091

; Minute 58

0x00a5

0x00b8

; Second 17

0x00c1

0x00d7

0x00e0

; Set Clock Time

```

# **NOTE:** If no timecode input is present (TPRO), or the GPS receiver is not tracking satellites (TSAT), the board will accept the time set sequence described above and continue to increment time ("freewheel").

However, when a valid timecode (TPRO) is input, or when the GPS receiver begins tracking satellites (TSAT), the clock's time will jump to the decoded time, unless the above sequence was preceded with a Disable Sync command (described later in this chapter).

While freewheeling, the In-Sync status bit will be false.

The user's software must ensure that the commanded values are in the appropriate ranges. The board does not error-check the data before loading the clock. Commanding invalid values (e.g., 39 hours) causes erratic operation.

# 7.7 Setting the Clock Time (TPRO Option -M Only)

Set the clock time by commanding the days, hours, minutes, and seconds. The milliseconds and microseconds cannot be commanded; they are reset to 000000 when the *next* 1PPS occurs. The clock time of the *next* 1PPS is commanded to the board.

It is necessary to load the time into the Holding Register. First, send a command to clear the Holding Register. Then, one at a time, write each digit (hundreds of days down to ones of seconds) into the Holding Register.

There is a separate command for loading each of these digits. The upper 4 bits of the command identify which digit is being loaded, the lower 4 bits contain the actual data to load. Once all the digits have been loaded, a command is sent to arm the clock.

For example, to set the clock to day 123, hour 11, minute 58, second 17, send the following sequence of commands to the Command Port:

```

0x00f0

; Clear the Holding Register

0x0051

0x0062

0x0073

; Day 123

0x0081

0x0091

; Hour 11

0x00a5

0x00b8

; Minute 58

0x00c1

0x00d7

; Second 17

; Arm the clock for next 1PPS

0x004c

```

After sending the 0x004c command, the board sets the milliseconds and microseconds to 000000 when the first 1PPS occurs (the seconds do not increment). Then, on the second 1PPS pulse, the time (seconds) begins to increment.

#### **CAUTION:**

The board expects the 1PPS input to be continuous. If the 1PPS signal stops pulsing after the board establishes initial sync, the board will continue to increment time ("freewheel"). However, if the 1PPS signal resumes after a period of freewheeling, the board may reset the clock time to 000:00:00:00:0000000. This is because the 1PPS occurs outside of a narrow window in which the board expects it, either because the 1PPS has moved or because the board's time has drifted during freewheeling.

The arm command (0x004c) must be sent no sooner than 50 mS after the previous 1PPS occurred, and no later than 50 mS before the next (arming) 1PPS occurs.

**NOTE:** If both 1PPS and Timecode inputs are present, the board will sync to the incoming timecode and ignore the 1PPS.

Commands 0x004d and 0x004e (Enable/Disable Sync) apply both to the 1PPS and the timecode input. Commands 0x00e0 (set clock) and 0x00ea (set year) are not applicable to boards with Option –M.

The user's software must ensure that the commanded values are in the appropriate ranges. The board does not error-check the data before loading the clock. Commanding invalid values (e.g., 39 hours) will cause erratic operation.

## 7.8 Setting the Year (Not Applicable to Option -M)

Whether the IRIG-B output is synchronized to GPS or timecode, or is freewheeling, it counts from day 365 to day 001, unless the year is set to a leap year. Once set to a leap year, the IRIG-B output counts from 365 to 366, then to 001.

The TSAT acquires the year from the GPS satellites. The year can also be set by command (if the GPS receiver is not connected).

To function properly, the TPRO requires that the year be set by command at the end of a leap year. The board will increment the year when the day rolls over to 001. Also, setting the year enables the board (TPRO and TSAT) to compute the Gregorian date using the year and Julian date.

Set the year by sending the command sequence "0x006n 0x007n 0x008n 0x009n 0x00ea" to the command port. For example, to set the year to 2003, send "0x0062 0x0070 0x0080 0x0093 0x00ea".

The year is reset to 0000 when power is first applied, or when any of the following occur: system reset, firmware reset (command 0x004f), or writing to the "Assert Reset" or "De-assert Reset" addresses.

# 7.9 Reading the Year, Gregorian Date and Altitude (Not Applicable to Option -M)

The GPS receiver's computations for the altitude (TSAT only) and Gregorian date (TSAT and TPRO) are reported in the FIFO in response to the 0x005d command. Altitude is in units of meters relative to mean sea level.

| Word      | Bits 7-4                | Bits 3 – 0             |

|-----------|-------------------------|------------------------|

| 0 (first) | 5                       | D                      |

| 1         | 5                       | D                      |

| 2         | 10 <sup>1</sup> Day     | 10 <sup>0</sup> Day    |

| 3         | 10 <sup>5</sup> meters  | 10 <sup>4</sup> meters |

| 4         | 10 <sup>3</sup> meters  | 10 <sup>2</sup> meters |

| 5         | 10 <sup>1</sup> meters  | 10 <sup>0</sup> meters |

| 6         | 10 <sup>-1</sup> meters | 0                      |

| 7         | 10 <sup>1</sup> Year    | 10 <sup>0</sup> Year   |

| 8         | 10 <sup>3</sup> Year    | 10 <sup>2</sup> Year   |

| 9 (last)  | 10 <sup>1</sup> Month   | 10 <sup>0</sup> Month  |

The board increments the Gregorian date approximately one second after time rolls over from 23:59:59 to 00:00:00 (HH:MM:SS). This occurs on every date in every year. Consequently, the Gregorian date should not be used during minutes 59 and 00—this will avoid rollover problems.

# 7.10 Report Longitude (TSAT Only)

The GPS receiver's computation for longitude is put into the FIFO in response to the 0x005e command. The units are degrees, minutes, and fractions of minutes. The response is in the following format:

| Word      | Bits 7-4                 | Bits 3-0                 |

|-----------|--------------------------|--------------------------|

| 0 (first) | 5                        | е                        |

| 1         | 5                        | е                        |

| 2         | 0                        | 10 <sup>2</sup> Degrees  |

| 3         | 10 <sup>1</sup> Degrees  | 10 <sup>0</sup> Degrees  |

| 4         | 10 <sup>1</sup> Minutes  | 10 <sup>0</sup> Minutes  |

| 5         | 10 <sup>-1</sup> Minutes | 10 <sup>-2</sup> Minutes |

| 6         | 10 <sup>-3</sup> Minutes | 10 <sup>-4</sup> Minutes |

| 7         | Reserved                 | Reserved                 |

| 8         | Reserved                 | Reserved                 |

| 9 (last)  | Reserved                 | Reserved                 |

**NOTE:** If the reported value is less than 180 degrees, the longitude is East (for Europe, Africa, Asia, etc.). If the reported value is greater than or equal to 180 degrees, subtract 180 degrees to obtain west longitude (for USA, Canada, Central & South America, etc.). For example, the reported value for Los Angeles, CA, USA, will be approximately 298 degrees. Since this is greater than 180, subtract 180 to get the correct value, i.e., 118 degrees West. Be sure to convert minutes to decimal degrees before comparing to 180 degrees.

# 7.11 Report Latitude (TSAT Only)

The GPS receiver's computation for latitude is put into the FIFO in response to the 0x005f command.

The units are degrees, minutes, and fractional minutes. Latitudes north of the equator are reported as 0–90 degrees, latitudes south of the equator are reported as 180+ degrees South—i.e., if the reported value is greater than or equal to 180, subtract 180 degrees and change the sign to negative (south). It is important to convert minutes to decimal degrees before comparing to 180 degrees. The response is in the format shown here:

| Word      | Bits 7–4                 | Bits 3-0                 |

|-----------|--------------------------|--------------------------|

| 0 (first) | 5                        | f                        |

| 1         | 5                        | f                        |